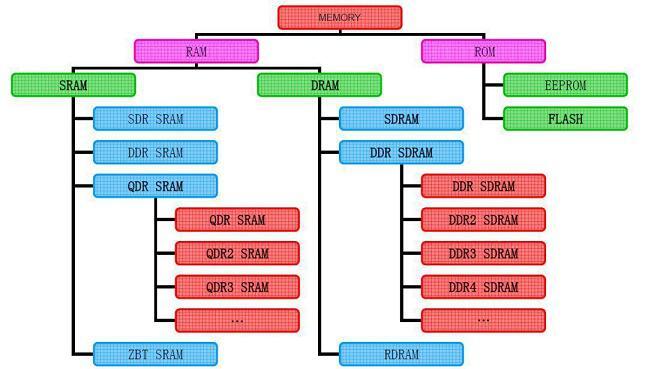

우리가 컴퓨터 구조에서 항상 얘기하는 '메모리'는 통상적으로 RAM(Random Access Memory)입니다. RAM의 크기를 식탁의 크기라고 비교해본다면, 반찬이 있는 냉장고는 하드디스크, 식탁에 있는 음식을 먹는 사람은 CPU라고 할 수 있습니다. 식탁의 크기가 클수록 한번에 먹을 수 있는 음식이 많아지겠죠. 그리고 식사 속도는 CPU의 성능에 비유될 수 있습니다. RAM에 대해 자세히 알아보시죠.

DRAM(Dynamic RAM)

DRAM의 Dynamic은 저장된 데이터가 동적으로 사라지는 RAM을 의미합니다. DRAM은 시간이 지나면 저장된 데이터가 점차 사라지는 RAM입니다. 그렇기 때문에 DRAM은 데이터의 소멸을 막기 위해 주기적으로 데이터를 재활성화(다시 저장)해야 합니다.

그럼에도 불구하고 일반적으로 사용되는 메모리는 DRAM입니다. 소비 전력이 낮고 저렴하며 집적도가 높기 때문이죠. DRAM은 주로 개인 컴퓨터 및 서버에서 사용되는 일반적인 RAM 형태입니다.

SRAM(Static RAM)

SRAM은 DRAM과 다르게 저장된 데이터가 변하지 않습니다. 주기적으로 데이터를 재활성화할 필요도 없죠.SRAM은 전하를 계속 유지하므로 재충전이 필요하지 않습니다. 이로 인해 DRAM보다 더 빠르지만, 더 많은 공간을 차지하고 더 비싸다는 단점이 있습니다(소비전력도 크며 집적도가 낮습니다). 따라서 대용량으로 만들 필요가 없지만 고성능이 필요한 캐시 메모리로 사용됩니다.

SDRAM(Synchronous Dynamic RAM)

SDRAM은 DRAM의 단점을 보완한 RAM입니다. SDRAM은 클럭 신호와 동기화되어 클럭 타이밍에 맞춰 CPU와 정보를 주고 받을 수 있습니다. CPU와 동기화되었기 때문에 SDRAM이라고 불립니다.

DDR SDRAM(Double Data Rate SDRAM)

DDR SDRAM은 대역폭을 넓혀 속도를 빠르게 만든 SDRAM입니다. 여기서 대역폭이란 데이터를 주고받는 길의 넓이를 말합니다. 클럭 한번에 한 번씩 CPU와 데이터를 주고 받을 수 있는 SDRAM에 비해 DDR SDRAM은 두 배의 대역폭으로 한 클럭당 두 번씩 CPU와 데이터를 주고 받을 수 있습니다. DDR, DDR2, DDR3, DDR4, DDR5 등의 세대가 있으며, 각 세대마다 더 높은 데이터 전송 속도와 더 낮은 전력 소비를 지원합니다.

'컴퓨터 일반' 카테고리의 다른 글

| [보조기억장치] 하드 디스크와 플래시 메모리 (0) | 2023.10.11 |

|---|---|

| 물리주소(Physical Address)와 논리주소(Logical Address) (0) | 2023.10.11 |

| 레지스터란? (0) | 2023.10.08 |

| 아스키코드(ASCII)가 128개밖에 없는 이유 (0) | 2023.10.07 |

| 10진수 -> 2진수/16진수 변환(2진수/16진수 -> 10진수 변환) (2) | 2023.10.05 |

댓글